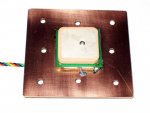

Rob:

Hast du schon mal versucht aus einem Ublox die Daten nicht seriell sondern gleich als I2C abzurufen ? Die Module haben offenbar auch eine I2C Schnittstelle die nennt sich da DDC . Ich weis ja nicht welche daten du verarbeitest und welche da kommen, aber würde das den zusätzlichen Prozessor überflüssig machen ?

Steht hier:

http://www.u-blox.com/images/downlo...DescriptionProtocolSpec_(GPS.G6-SW-10018).pdf

http://www.u-blox.com/images/stories/linecards_u-blox_gps_modules_2012.pdf

Hast du schon mal versucht aus einem Ublox die Daten nicht seriell sondern gleich als I2C abzurufen ? Die Module haben offenbar auch eine I2C Schnittstelle die nennt sich da DDC . Ich weis ja nicht welche daten du verarbeitest und welche da kommen, aber würde das den zusätzlichen Prozessor überflüssig machen ?

Steht hier:

http://www.u-blox.com/images/downlo...DescriptionProtocolSpec_(GPS.G6-SW-10018).pdf

Code:

[COLOR=#222222][URL="http://www.u-blox.com/images/stories/linecards_u-blox_gps_modules_2012.pdf"]4.3 DDC Port

[/URL][/COLOR]A Display Data Channel (DDC) bus is implemented, which is a 2-wire communication interface compatible with

the I2C standard (Inter-Integrated Circuit). See our online product selector matrix for availability.

Unlike all other interfaces, the DDC is not able to communicate in full-duplex mode, i.e. TX and RX are mutually

exclusive. u-blox receivers act as a slave in the communication setup, therefore they cannot initiate data

transfers on their own. The host, which is always master, provides the data clock (SCL), and the clock frequency

GPS.G6-SW-10018-A Public Release Page 8 of 201

is therefore not configurable on the slave.

The clock rate on the SCL line generated by the master must not exceed 100kHz (standard-mode).

The receiver's DDC address is set to 0x42 by default. This address can be changed by setting the mode field in

CFG-PRT for DDC accordingly.

As the receiver will be run in slave mode and the physical layer lacks a handshake mechanism to inform the

master about data availability, a layer has been inserted between the physical layer and the UBX and NMEA

layer. The DDC implements a simple streaming interface that allows the constant polling of data, discarding

everything that is not parseable. This means that the receiver returns 0xFF if no data is available. With firmware

7.01 the TX-ready feature was introduced to inform the master about data availability. It can be used as a

trigger for data transmission.

If no data is polled for 2 seconds, the interface is assumed to be idle. The receiver clears all pending data and

no new messages will be scheduled to this interface. This mechanism can be disabled using the extended TX

timeout flag in the port configuration, which allows longer time without bus read access. Note that interface

[COLOR=#222222][URL="http://www.u-blox.com/images/stories/linecards_u-blox_gps_modules_2012.pdf"]data will be deleted when the internal buffer limit of 4 kB is exceeded.

[/URL][/COLOR]http://www.u-blox.com/images/stories/linecards_u-blox_gps_modules_2012.pdf